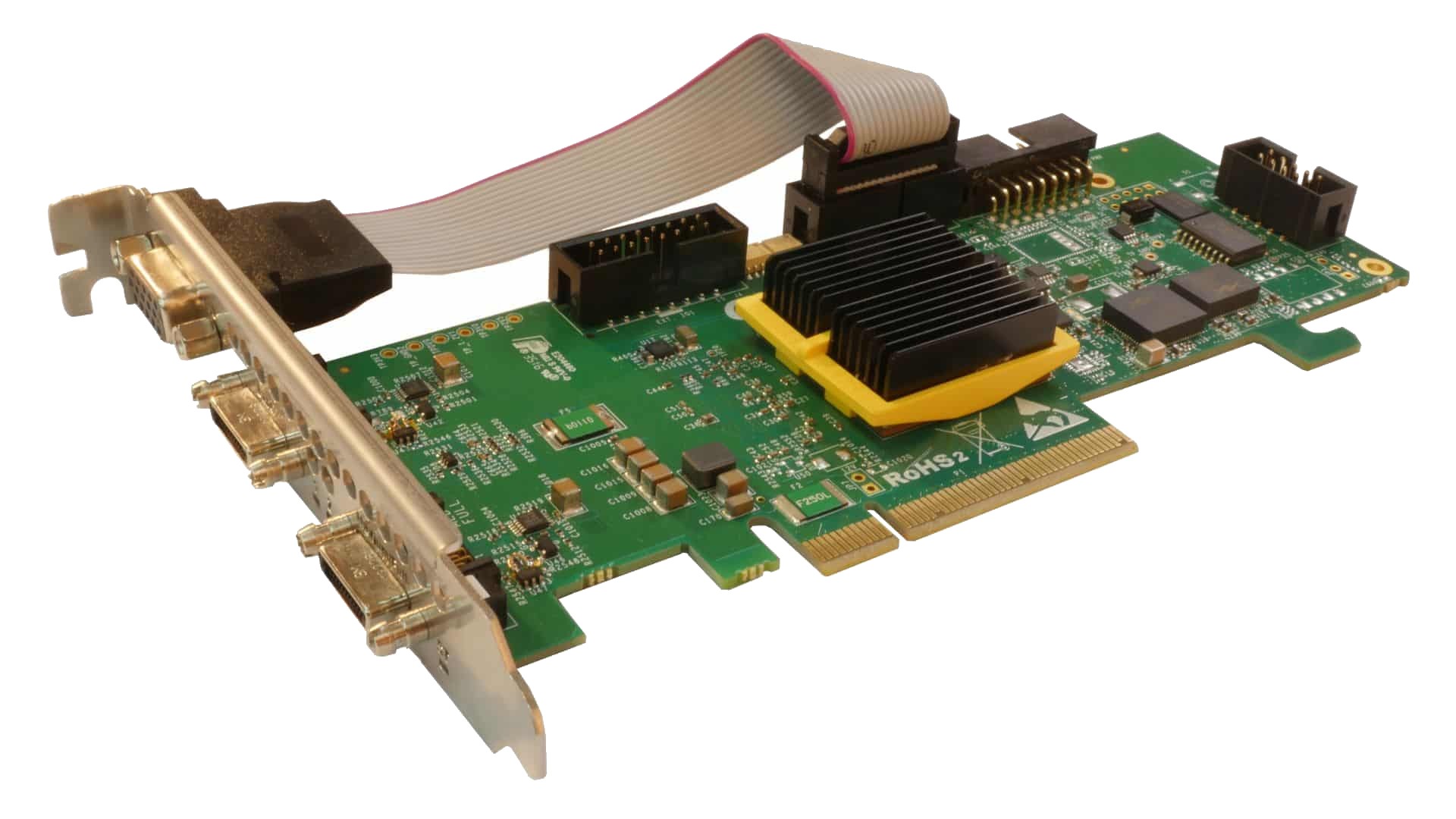

The Gidel HawkEye-CL is a high-performance Camera Link frame grabber with FPGA image processing designed for real-time, high-throughput machine vision applications. Unlike traditional Camera Link frame grabbers, the HawkEye-CL integrates FPGA-based inline processing for real-time image analysis.

Built on Intel Arria 10 FPGA technology and a PCIe Gen3 x8 interface, this Camera Link 2.0 frame grabber delivers ultra-fast image acquisition, low-latency inline / on-the-fly processing for demanding industrial, scientific, and defense imaging systems.

The HawkEye-CL is fully Camera Link 2.0 compliant, supporting Base, Medium, Full, and 80-bit (Deca) configurations for maximum bandwidth and precision. On-board memory up to 16 GB enables high-capacity image buffering and sustained high-speed acquisition. The HawkEye-CL is available as a PCIe frame grabber board or as part of a complete FPGA-based vision system. Using Gidel’s InfiniVision architecture, the system can scale to support 100+ synchronized cameras in complex multi-camera systems.

The HawkEye-CL FPGA Camera Link FPGA frame grabber ( and all Gidel FPGA frame grabbers) enable true inline / on-the-fly image processing, including advanced compression (JPEG, Lossless, and Quality+), HDR correction, dynamic image enhancement, and fully customizable FPGA pipelines. Gidel's innovative architecture allows high-speed data reduction and real-time processing while significantly reducing CPU load and system latency – features that set this FPGA Camera Link frame grabber apart from traditional frame grabbers.

Gidel offers a full range of FPGA frame grabbers and vision platforms, from cost-effective off-the-shelf boards to high-performance, application-specific solutions supporting Camera Link, CoaXPress, and 10GigE Vision interfaces. To accelerate development, Gidel provides the InfiniVision and ProcFG SDKs, featuring comprehensive APIs, libraries, and graphical tools for FPGA image processing, compression, and multi-camera system design.

Contact us to explore Gidel's diverse frame grabber offerings and determine if a standard or custom-engineered solution is the ideal fit for your specific needs.

HawkEye-CL Frame Grabber Datasheet

HawkEye-CL Frame Grabber Datasheet

| Camera Input | 1x 80-bit (Deca), Full, Medium or Base Camera Link Dual Base Optional: protocol |

|---|---|

| Camera Link Compliant | Camera Link Rev. 2.0 |

| Camera Input Connectors | 2x SDR26 (mini Camera Link) |

| Additional Connectors | VGA15-pin for connecting GPIO's via cable to the bracket 16-pin board-to-board header JTAG |

| Advanced ROI feature | on-the-fly selective ROI acquisition |

| Image Formats | Mono, Bayer, RGBA (8, 10, 12, 14 and 16 bits/color) RGB (8, 10 and 12 bits/color) |

| Max. Resolution | Horizontal: 16 K pixels (64-bit) Vertical: 65 K lines |

| Tap Configuration | All configurations as defined by the Camera Link standard, including 80-bit (Deca): 10 taps/8bits, 8bits/10taps. |

| Maximum Acquisition Throughput | 6.8 Gb/s |

| Compression & Image Enhancements |

Compression Options: .JPEG, Lossless, Quality+

Image Enhancements Options: High Dynamic Range (HDR) correction For more modular image-processing options Contact Us |

| Pixel Clock | Up to 85 MHz |

| Host Bus | PCIe x 8 Gen. 3 |

| On Board Memory | Up to 16 Gb |

| Camera Types |

Area Line Scan |

| Form Factor | Full-height, single-slot, half-length PCIe card |

| GPIO | GPIO #1:

4 X RS422 INPUTS

Optional input clk 1x Optocoupler input GPIO #2:

1 X RS422 INPUTS

GPIO #3 (for board-to-board connection):

2x Opto-coupler inputs 2X 3-30V @ 0.8A outputs LVTTL IO 12V/1A power supply

12x LVTTL IO (5V TTL tolerant)

|

| Power | 5-32W: Depends on user application and FPGA Type |

| Cooling | Passive cooling | Active cooling (fan) |

| MTBF | Passive colling:

3.5M hours

Active colling:

HE CL-48 > 400K hours

HE CL-16 > 500K hours |

| Temperature | Operating ambient air temperature: 0 - 55° C |

|---|---|

| Humidity | Continuous Operation: 10 - 80% (non-condensing) Peak Operation: 10 - 90% (non-condensing) |

| Environmental Compliance |

RoHS Conflict Minerals ISO Reach |

| Real-Time Image Processing |

Gidel FPGA flow can integrate advanced image processing algorithms, including:

Compression encoders: JPEG | Lossless | Quality+

High Dynamic Range (HDR) correction from a single exposure White Balance - Maintains color accuracy across variable lighting conditions Dynamic Luminance Balance - Preserves consistent brightness under changing illumination Morphological operations such as Open/Close using a round structuring element |

|---|---|

| User FPGA code | Users can integrate their own FPGA code with Gidel’s IPs |

| Form Factor | Low profile (Comes without the IO connector) |

Contact us if you need a customized solution!

Grabbers SDK

Application Interfaces

Software Compatibility